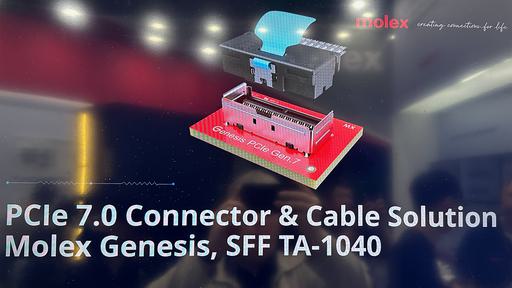

Molex showcased its Genesis cabling solution for PCIe 7.0 at Computex, delivering 128 GT/s data transfer rates at distances up to 1 meter while addressing the limitations of traditional PCB traces in high-speed applications.

G. Ostrov

Molex, a specialist in connector manufacturing, demonstrated its advanced Genesis cabling solution for the PCIe 7.0 standard at the Computex exhibition, capable of delivering 128 GT/s data transfer rates at distances up to one meter.

Overcoming PCB Trace Limitations

PCIe cables like Molex's Genesis address challenges posed by high-speed signaling and the limitations of traditional PCB traces in terms of signal integrity and trace lengths. Genesis utilizes an SFF TA-1040 connector for compatibility and potential broad industry adoption as PCIe 7.0 infrastructure begins deployment.

Superior Signal Integrity Performance

Molex's proprietary signal integrity simulations for Genesis demonstrate controlled performance across various cable lengths. At 32 GHz, insertion loss ranges from -3.4 dB at 250 mm to -9.2 dB at 1000 mm, showcasing effective signal retention over extended distances. Crosstalk levels remain low across all lengths up to 1000 mm, with tight impedance control maintained throughout connector and cable assemblies.

Technical Specifications

Genesis is engineered for structural reliability, minimal footprint suitable for densely packed servers, and support for cable lengths up to 1000 mm without compromising signal integrity. This is achieved through 29 AWG low-loss microwave coaxial cables optimized for high-frequency performance, signal integrity, and reliability.

Product Roadmap

Molex's roadmap for Genesis includes the x8 connector scheduled for May 2025, the x16 model in July 2025, and a future x20 version. The Genesis design supports up to 74 pins for x8 configurations, with larger x16 and x20 variants planned to accommodate 124 and 148 pins respectively. Multiple orientation options are planned, including right-angle, angled-exit, and vertical-exit designs.

Form Factor Details

The connector widths scale with lane count: 28 mm for x8, 47 mm for x16, and 57 mm for x20 configurations. All connectors feature a standardized height of 8.7 mm and depth of 13.2 mm, catering to dense system design requirements while maintaining optimal performance characteristics.

Industry Timeline

The PCIe 7.0 specification is currently at final draft version 0.9, with PCI-SIG expected to deliver the final PCIe 7.0 specification 1.0 this year. Even with datacenter-grade hardware fully adopting PCIe 6.0 by 2026-2027, PCIe 7.0 adoption is expected to begin either very late this decade or in the early 2030s.

For more information about the company's products, visit the official Molex website.